计算机体系结构中的流水线技术 迈向高性能计算系统集成的关键

在计算机体系结构的演进历程中,流水线技术无疑是提升处理器性能的核心技术之一。它借鉴了工业生产中流水线的思想,将指令执行过程分解为多个相互独立但又紧密衔接的阶段,允许多条指令在同一时刻处于不同的执行阶段,从而显著提高了指令吞吐率,实现了从串行执行到并行处理的跨越。

流水线技术的基本原理在于将复杂的指令执行过程细分为取指、译码、执行、访存和写回等多个阶段。每个阶段由专门的硬件功能部件负责,当一条指令完成一个阶段后,便进入下一个阶段,同时下一条指令可以立即进入刚刚空出的阶段。这种时间上的重叠,使得从宏观上看,处理器几乎每个时钟周期都能完成一条指令的执行,极大地提升了效率。经典的5级流水线(MIPS架构)便是这一思想的典范。

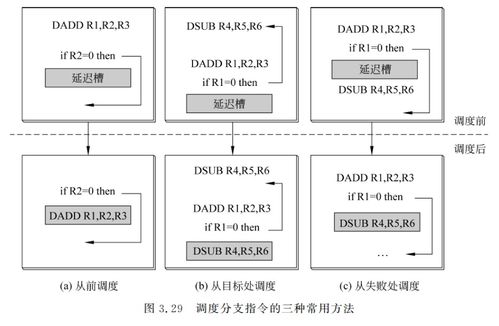

流水线的设计并非一帆风顺,其面临的主要挑战是各种“冒险”(Hazard)。结构冒险源于硬件资源冲突,例如访存阶段单一内存端口的争用;数据冒险则发生在指令间存在数据依赖时,后续指令需要等待前序指令产生结果;控制冒险则是由分支指令引起的,处理器需要预测下一条指令的地址,预测失败则会导致流水线清空,产生性能损失。为了解决这些问题,现代处理器集成了诸如转发技术(旁路)、分支预测器、乱序执行以及更深的流水线等复杂机制。

流水线技术的深度发展,直接推动了计算机系统的集成。在芯片内部,更复杂、更深的流水线设计需要集成更多的功能单元、更庞大的寄存器堆和更智能的控制逻辑,这促进了微处理器内部的高度集成与复杂化。在系统层面,为了充分发挥流水线处理器的性能,需要与之匹配的高速缓存(Cache)层次结构、高带宽内存子系统以及高效的输入输出(I/O)通道。内存墙(Memory Wall)问题——即处理器速度远快于内存访问速度——成为系统集成设计中必须攻克的关键瓶颈。通过集成多级缓存、更宽的内存总线和更先进的内存技术(如DDR、HBM),系统设计者致力于为流水线提供持续稳定的数据流。

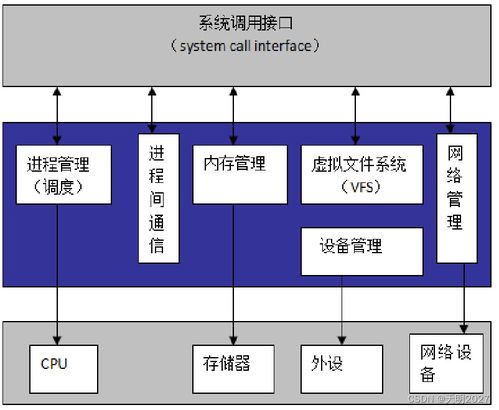

流水线思想也超越了CPU本身,影响了整个计算系统的集成架构。在现代图形处理器(GPU)中,大规模并行流水线(流处理器阵列)是其高性能计算的基石。在网络处理器和专用集成电路(ASIC)中,流水线设计也被广泛用于实现高速数据包处理和特定算法加速。从单核到多核,再到众核和异构计算(如CPU+GPU),系统的集成复杂度不断提升,其核心目标之一就是管理好由众多流水线核心产生的并行任务流和数据流。

随着半导体工艺逼近物理极限,单纯依靠加深流水线级数来提升频率已面临功耗和收益的瓶颈。未来的计算机系统集成将更加注重“片上系统”(SoC)和“异构集成”,将CPU、GPU、AI加速器、高速互连网络等通过先进的封装技术(如Chiplet)集成在一起。在这种架构下,流水线技术将演化为更加灵活、可配置的形态,与任务调度、能效管理、存储层次等系统级技术深度融合,共同支撑起下一代高性能、高能效的计算平台。

流水线技术不仅是处理器微架构的经典设计,更是驱动整个计算机系统向更高性能、更紧密集成方向发展的核心引擎。从指令级的并行到系统级的协同,它深刻地塑造了现代计算的面貌。

如若转载,请注明出处:http://www.qingdong999.com/product/73.html

更新时间:2026-02-27 10:26:05